Persistent Memory

Updated: Oct 26th, 2023

持久内存出现的背景

背景1:存储介质的发展

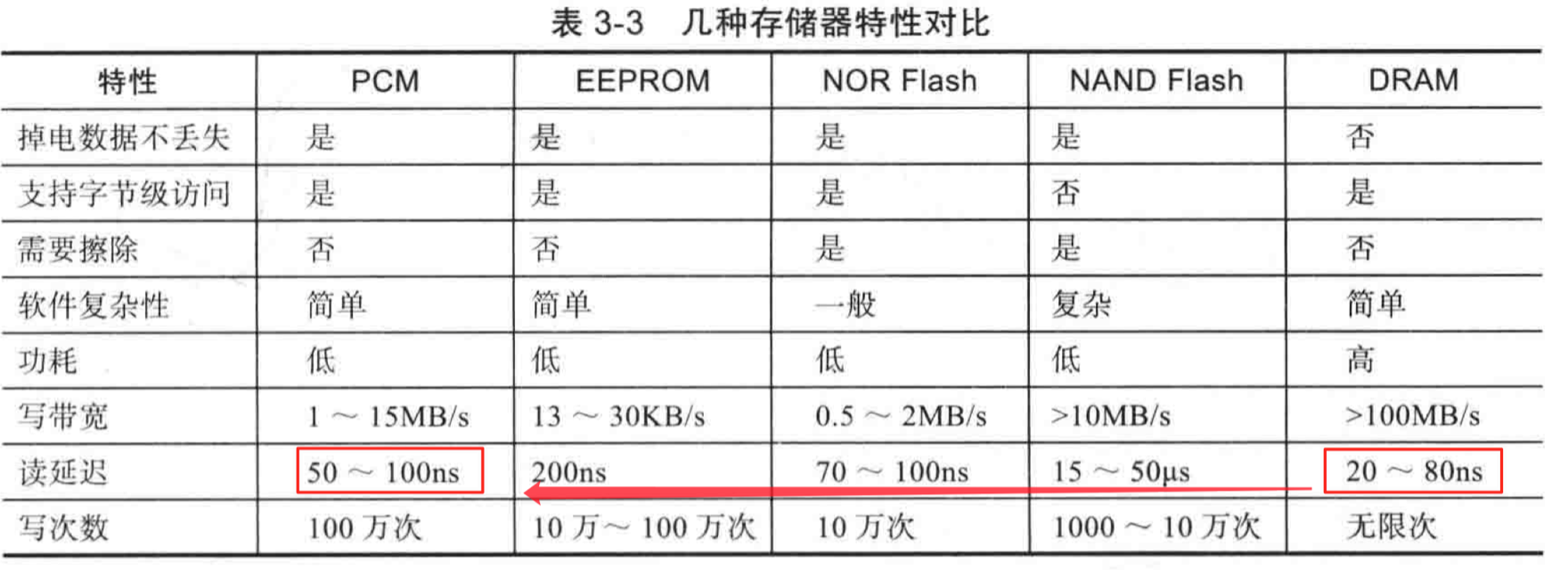

目前的存储介质延迟已经发展到ns级别了。如下图所示,PCM(Phrase-change Memory,相变内存)已经能够实现ns级别的读延迟,同时也达到了较高的寿命和较低的功耗,另外还支持字节级访问。

(图源:《深入浅出SSD》P94)

(图源:《深入浅出SSD》P94)

背景2:现有架构存在的问题

拿目前最快的持久存储设备,NVMe SSD为例,其使用了NVMe协议在PCIe总线上与CPU相连,延时最低能到10us左右。但考虑到PCIe总线本身就有0.8us左右的延时。随着存储介质的延时进一步减小至ns级别,PCIe总线上的延迟甚至超过了存储介质本身的延迟。这样的开销是难以接受的。

持久内存的特点

在上述两个背景之下,Intel首先推出了基于3D-XPoint的傲腾持久内存。

他具有下面三个特点:

- 与DRAM相近的读写延迟

- 可字节寻址

- 可持久存储

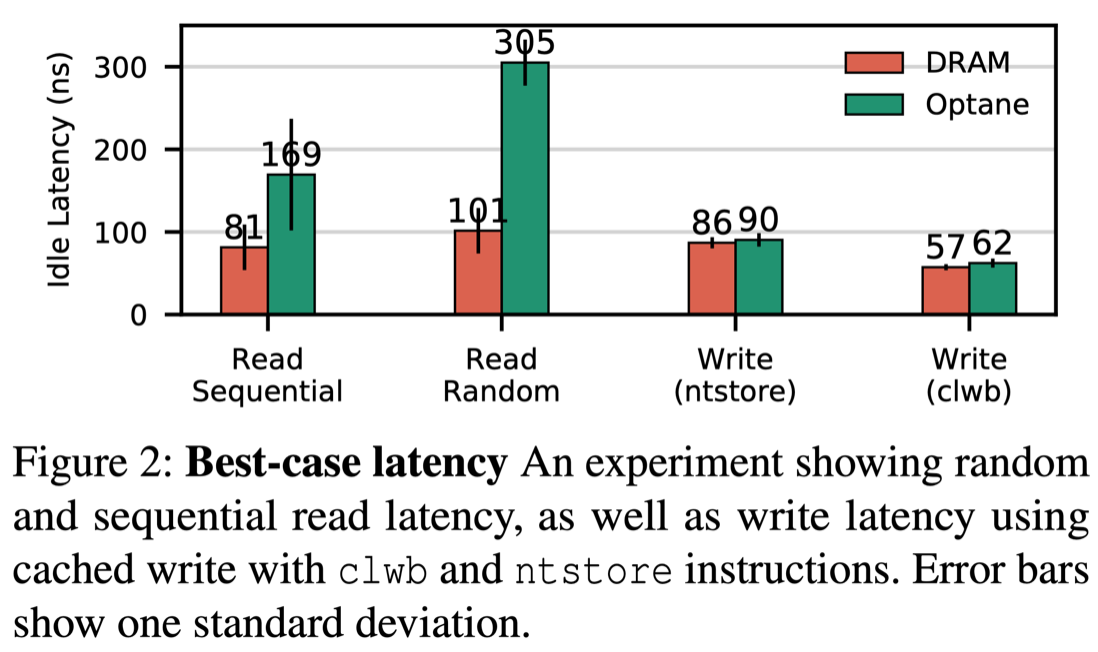

对于读写延迟来说,其与普通内存,也就是DRAM(Dynamic random-access memory, 动态随机存取存储器 )类似,在文章[1]中的一幅图中,可以发现非易失性内存无论是读延时还是写延迟,都比DRAM要慢一些,但数量级是相当的,所以我们可以概括说,延时和DRAM相当。

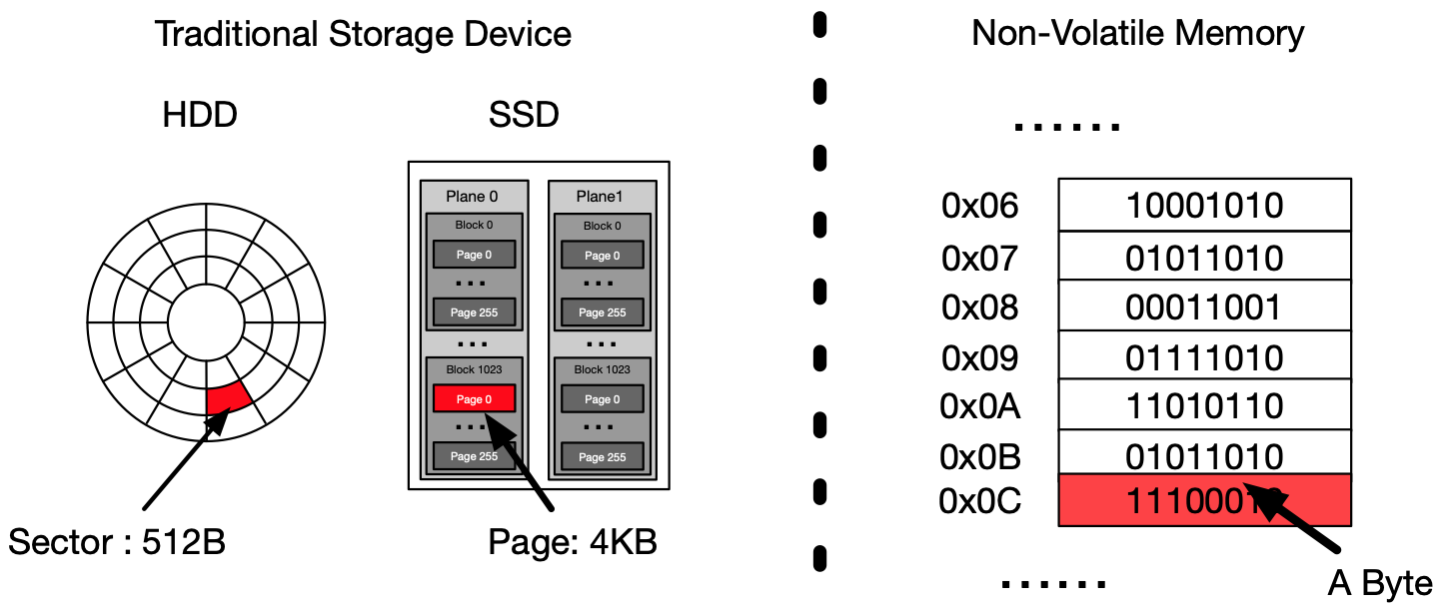

可字节寻址这个特点要和其他不同的存储介质进行对比。对于机械硬盘,其寻址的最小粒度是一个扇区,sector,一般是512B,而对于我们常见的固态硬盘,其寻址的最小粒度是一个page,一般是4KB。而对于非易失性内存,我们可以和内存一样,通过一个地址访问其每个字节的内容,访问的粒度是字节,这让非易失性内存和其他存储设备的区别更加大,编程模型要有较大的改变。

另外与DRAM非常不同的一点是,DRAM掉电了数据会丢失,而PM在掉电后数据仍然能够持久存储,在下次通电后数据还在。但非易失性内存直接接在内存插槽上,它又和普通的存储设备有些不一样的地方。这个不一样的地方来源于cpu的cache。我们执行了一条mov指令,在某个内存地址中存储某个数,那么这个数就并不一定存在了内存中,一般的cpu cache都采用了write back策略,意味着除非cache不够用了被置换了出来,否则这个数据很可能还在cache中,而cache本身仍然是断电就会丢数据的,这个时候就算下面安装了非易失性内存,也没法避免数据的丢失。所以,为了保证数据的持久性,我们需要使用一些额外的指令,比如图中的clflush,它的含义是将cache line刷写下来。为了避免CPU乱序执行的影响,我们还需要在这两条指令后面加一条mfence,内存屏障。这样下来,才能够保证整个持久化操作完成。

一些测试文章

这几篇是测试PM性能的