Controller Memory Buffers

Updated: Sep 21st, 2023

CMB首次在2014年NVMe1.2中提出。NVMe CMB是NVMe SSD上的一块内存空间,可以通过PCIe BAR的方式暴露到主机内存空间中,并可由主机直接读写。这一块内存空间可以用来放置一些NVMe上特定的数据结构(如 SQ,CQ等),也可以将需要传输的数据直接放在CMB中。下面来放一些CMB的实际使用例子以及其使用CMB的优势。

CMB 的功能

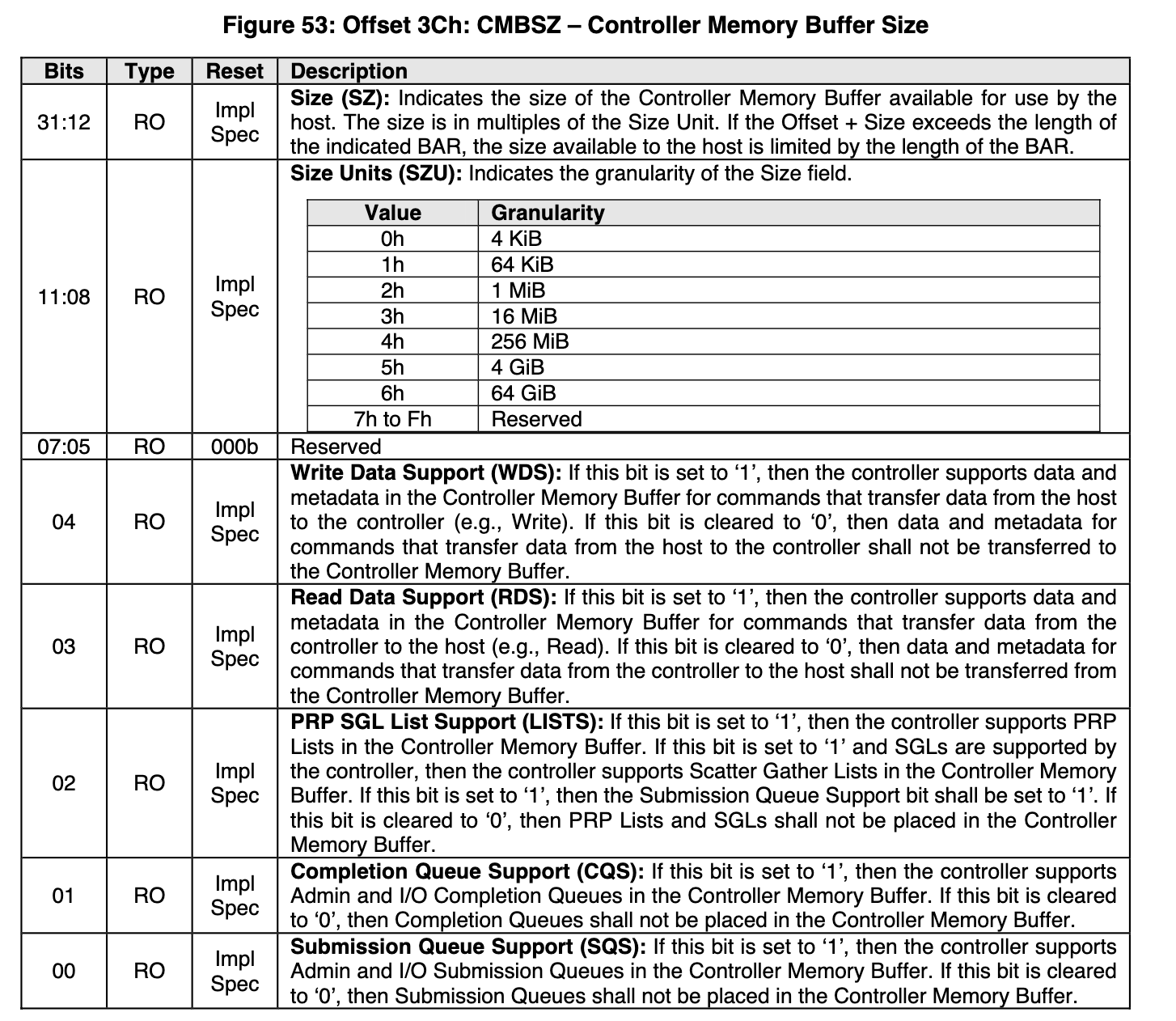

CMB 至少需要NVMe设备增加下面两个额外的寄存器,其中CMBLOC表示CMB的位置,CMBSZ表示CMB的大小,另外其中还附带了一些feature的标志位。关于这两个寄存器的细节可以阅读NVMe规范中的相关内容:

- 3.1.3.11 Offset 38h: CMBLOC – Controller Memory Buffer Location

- 3.1.3.12 Offset 3Ch: CMBSZ – Controller Memory Buffer Size

下图展示了CMBSZ中所包含的一些feature的介绍。

图源:Figure 53: Offset 3Ch: CMBSZ – Controller Memory Buffer Size

- Write Data Support (WDS): 对于将数据从主机写入到设备的命令(如Write),可以直接写入到CMB中。

- Read Data Support (RDS): 对于将数据从设备读取到主机的命令(如Read),可以直接从CMB中读取。

- PRP SGL List Support (LISTS): 可以将PRP和SGL放在CMB中。

- Completion Queue Support (CQS): 可以将CQ放在CMB中。

- Submission Queue Support (SQS): 可以将SQ放在CMB中。

使用CMB的例子

将CQ和SQ都放在CMB中。

- 以写SQ为例

- 原来是主机先把请求写到内存的SQ,然后写Doorbell通知SSD,然后SSD再从内存中的SQ将命令拷贝过来。

- 现在是主机直接写到CMB中的SQ,然后写Doorbell通知SSD。

- 两个相比较,后者少了一步写内存,将SQ放在CMB上降低了提交命令的延迟。

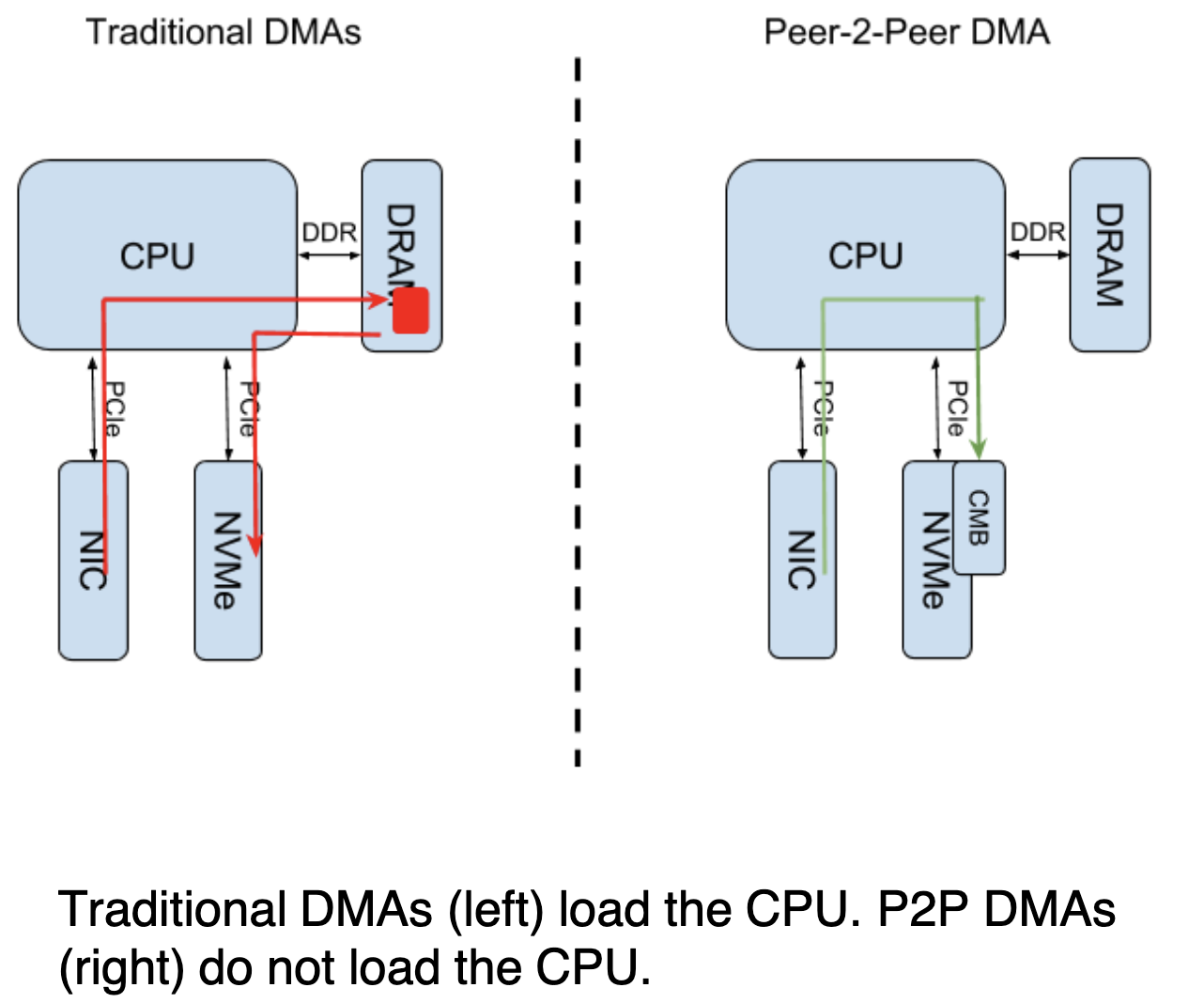

让CMB支持数据传输,优化NIC和NVMe SSD之间的数据传输。

原本将数据从NIC发送到SSD需要从内存中转一次,现在不需要,直接发送到CMB里就好。

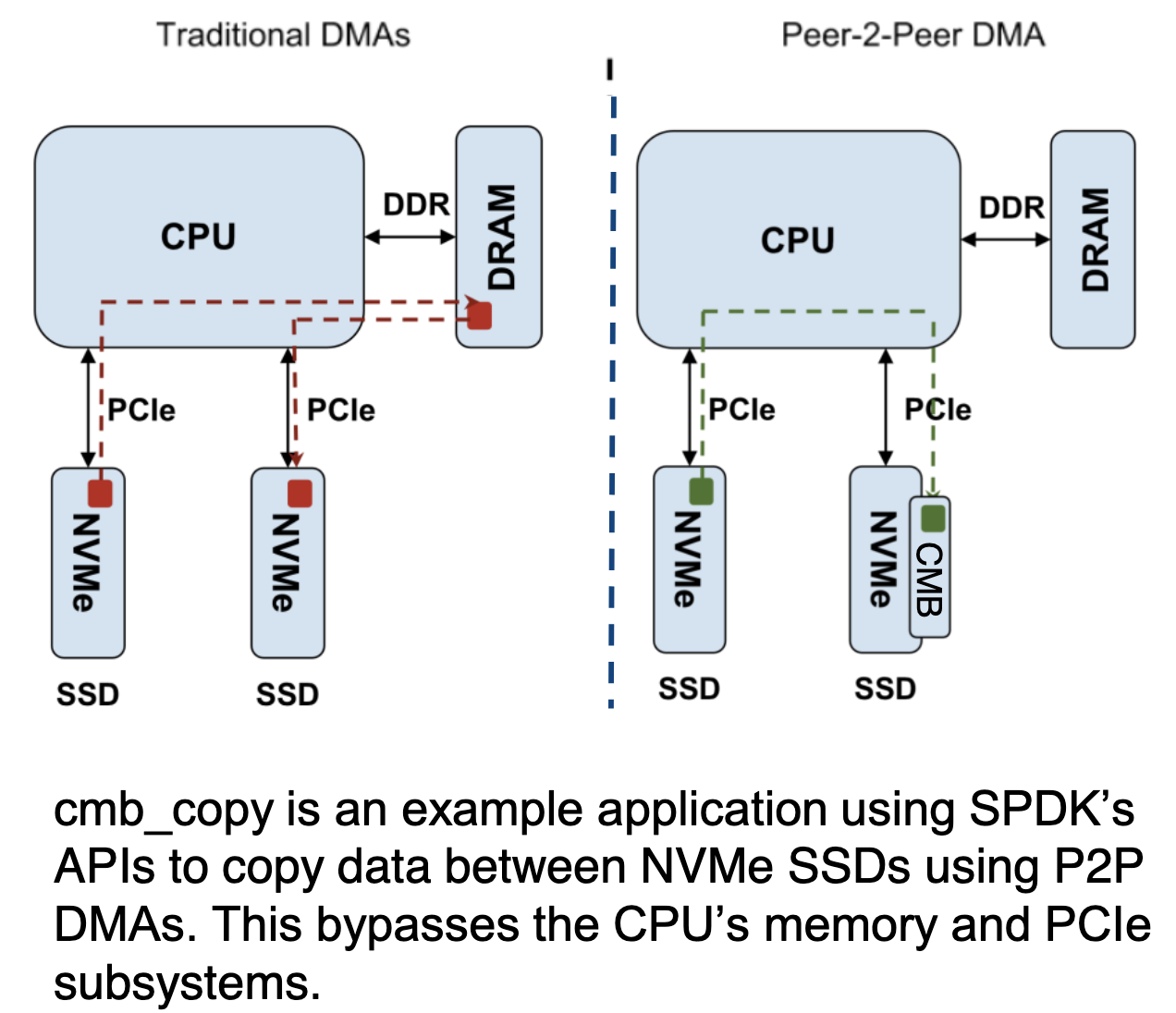

让CMB支持数据传输,优化NVMe SSD之间的数据传输。

利用了PCIe总线支持点对点通信的特点,在NVMe设备之间直接传数据到CMB上即可,完全无需CPU和内存的介入,也不需要Root Complex参与其中。

一些研究

典型工作:Horae[1]

相关资料

- Enabling the NVMe™ CMB and PMR Ecosystem

- Important new NVMe features for optimizing the data pipeline

- NVMe又有新花样!CMB vs HMB

- 一款支持CMB的固态:https://www.intel.com/content/www/us/en/products/docs/memory-storage/solid-state-drives/data-center-ssds/optane-ssd-dc-d4800x-series-brief.html

相关文献

[1]

X.

Liao, Y. Lu, E. Xu, and J. Shu, “Write Dependency Disentanglement

with {HORAE},” 2020, pp. 549–565 [Online]. Available: https://www.usenix.org/conference/osdi20/presentation/liao.

[Accessed: 24-Nov-2020]