PCI Express

Updated: Jan 11th, 2024

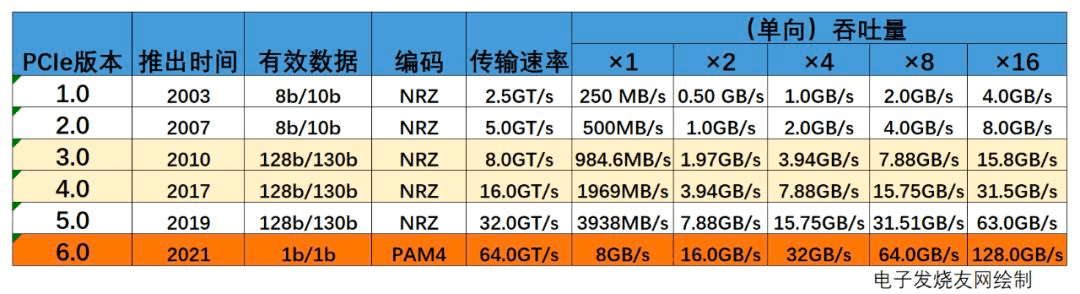

PCIe (Peripheral Component Interconnect Express) 是一种串行通信总线,其支持双单工模式通信1。由于PCIe速率更快,而且它的通用性较好,现在已经几乎取代了所有以往的内部总线。从2003年推出PCIe 1.0开始,PCIe单条lane单方向的带宽从0.25GB/s逐代翻倍。PCIe4.0单条lane的带宽已经达到2GB/s,现在2019年后PCIe 4.0已经出现在桌面设备中了。未来2022年支持PCIe 5.0的设备也将出现。

PCIe速率

该表参考自wiki

| PCI Express 版本 | 推出 | Line 编码 | 原始传输率 | 带宽(每个方向) | ||||

|---|---|---|---|---|---|---|---|---|

| ×1 | ×2 | ×4 | ×8 | ×16 | ||||

| 1.0 | 2003 | 8b/10b | 2.5 GT/s | 250 MB/s | 0.50 GB/s | 1.0 GB/s | 2.0 GB/s | 4.0 GB/s |

| 2.0 | 2007 | 8b/10b | 5.0 GT/s | 500 MB/s | 1.0 GB/s | 2.0 GB/s | 4.0 GB/s | 8.0 GB/s |

| 3.0 | 2010 | 128b/130b | 8.0 GT/s | 984.6 MB/s | 1.97 GB/s | 3.94 GB/s | 7.88 GB/s | 15.8 GB/s |

| 4.0 | 2017 | 128b/130b | 16.0 GT/s | 1969 MB/s | 3.94 GB/s | 7.88 GB/s | 15.75 GB/s | 31.5 GB/s |

| 5.0 | 2019 | NRZ 128b/130b | 32.0 GT/s | 3938 MB/s | 7.88 GB/s | 15.75 GB/s | 31.51 GB/s | 63.0 GB/s |

| 6.0 | 2021 | PAM4 & FEC 1b/1b | 64.0 GT/s | 8 GB/s | 16 GB/s | 32 GB/s | 64 GB/s | 128 GB/s |

(source)

(source)

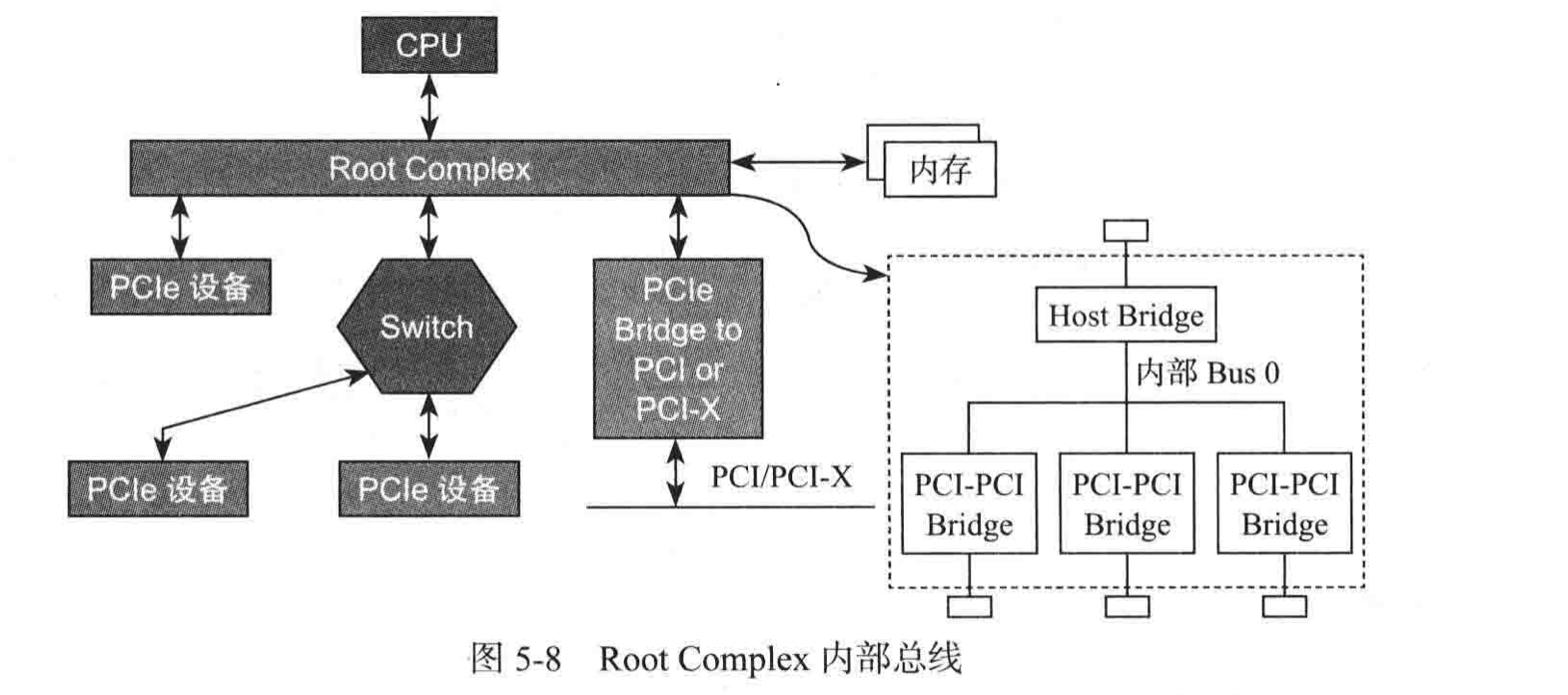

基于PCIe总线的计算机系统

PCIe采用树形拓扑接口,Root Complex是树的根,Switch是树枝,可以连接更多的Switch,也可以直接连接设备作为Endpoint。Endpoint之间使用点对点的通信方式,这意味着任意两个Endpoint时间都可以直接通信。实际上由于数据格式不一样,除非这两个Endpoint都是同一个厂商的,通常都是Endpoint与RC通信,或者是Endpoint通过RC与另一个Endpoint通信。

(图源《深入浅出SSD》P171)

(图源《深入浅出SSD》P171)

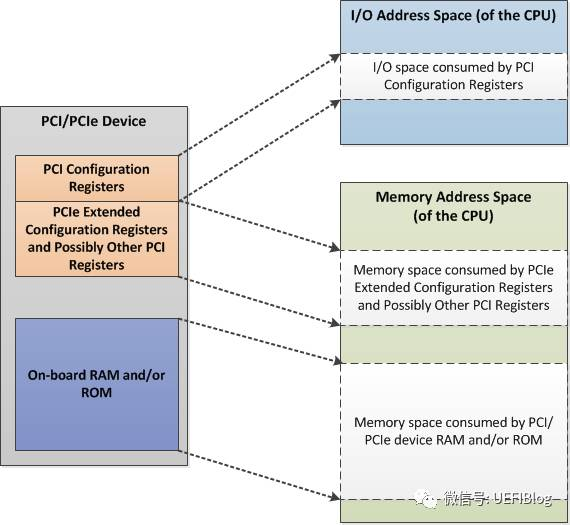

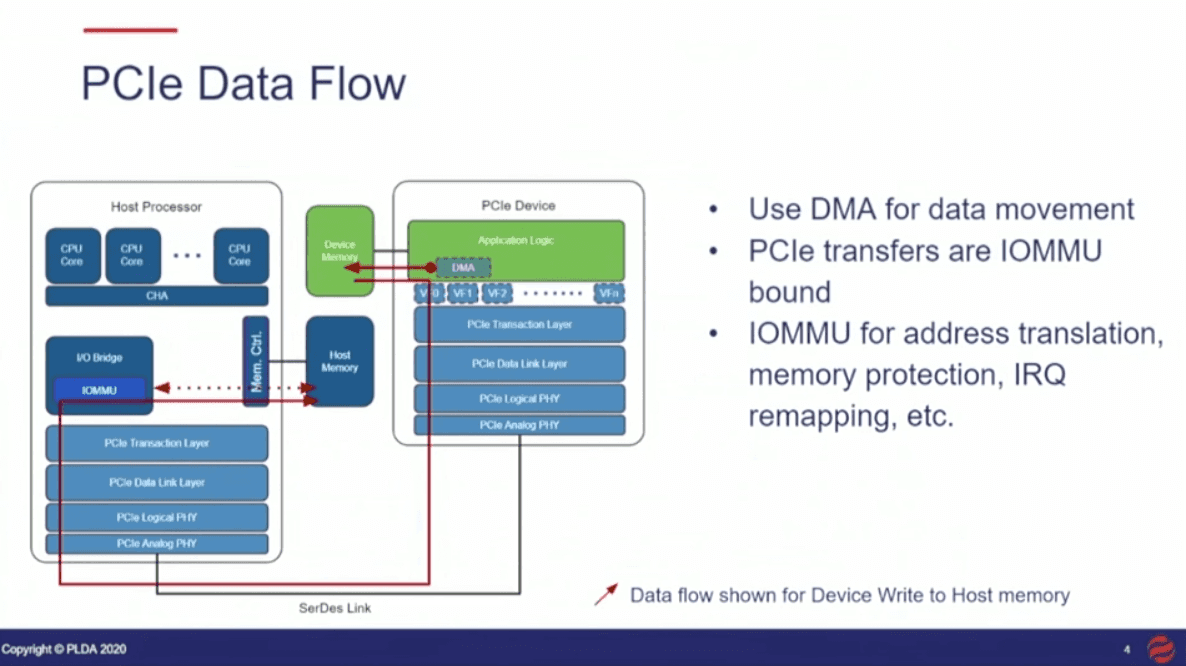

主机与PCIe设备间的通信

这里需要解释这两个问题: 1. PCIe设备上存储的信息,有哪些? 2. 主机如何访问PCIe设备上的信息? 3. 主机是如何读取PCIe设备上的信息的?

PCIe设备上存储的信息,有哪些?

PCIe设备上有一组Configuration Header,扩展的配置(可选),以及PCIe设备自身的内存或存储(如显存、闪存)(可选)。

(图源)

(图源)

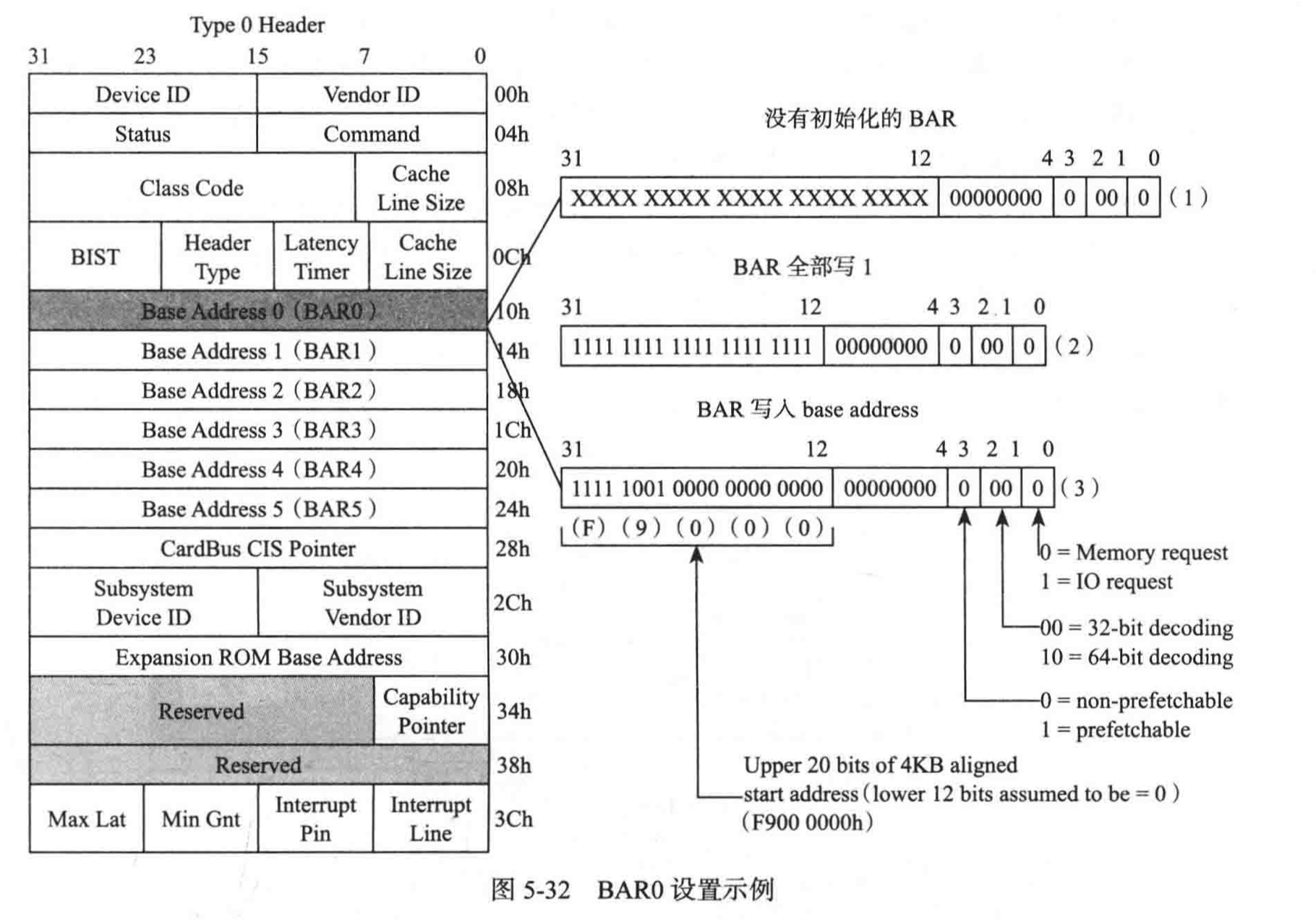

主机如何访问PCIe设备上的信息?

在PCIe Endpoint设备的Configuration Header中,有6个BAR(Base Address Register)。每个BAR在出厂时存储了PCIe设备中一个内存空间的大小以及相关固定参数,并留有一些空间写入内存空间基地址。主机读取该大小后,建立该空间与内存地址空间的映射,并将该内存地址空间的基地址写入到BAR中。

(图源:《深入浅出SSD》P187)

(图源:《深入浅出SSD》P187)

主机与PCIe设备之间的交互? |xxxx|xxxx| 对于PCIe Endpoint来说,这些信息通过MMIO映射到地址空间中,主机就可以像访问普通内存一样访问PCIe设备上的内容。这里需要注意: 1. 无论是读取PCIe设备还是写入PCIe设备,CPU都不直接与PCIe设备做交互。在读取时CPU会让Root Complex读取相关信息并写到BAR指定的内存区域中,在写入时则是CPU先将相关内容写入BAR指定的内存区域,然后再让Root Complex将数据从指定的内存区域写到PCIe设备里。 2. 有些内存空间是可以prefetch的,有些内存空间是不可以prefetch的。有些空间不可以prefetch,是因为有些寄存器一旦读取,其内部的数据就会被修改。

IOMMU

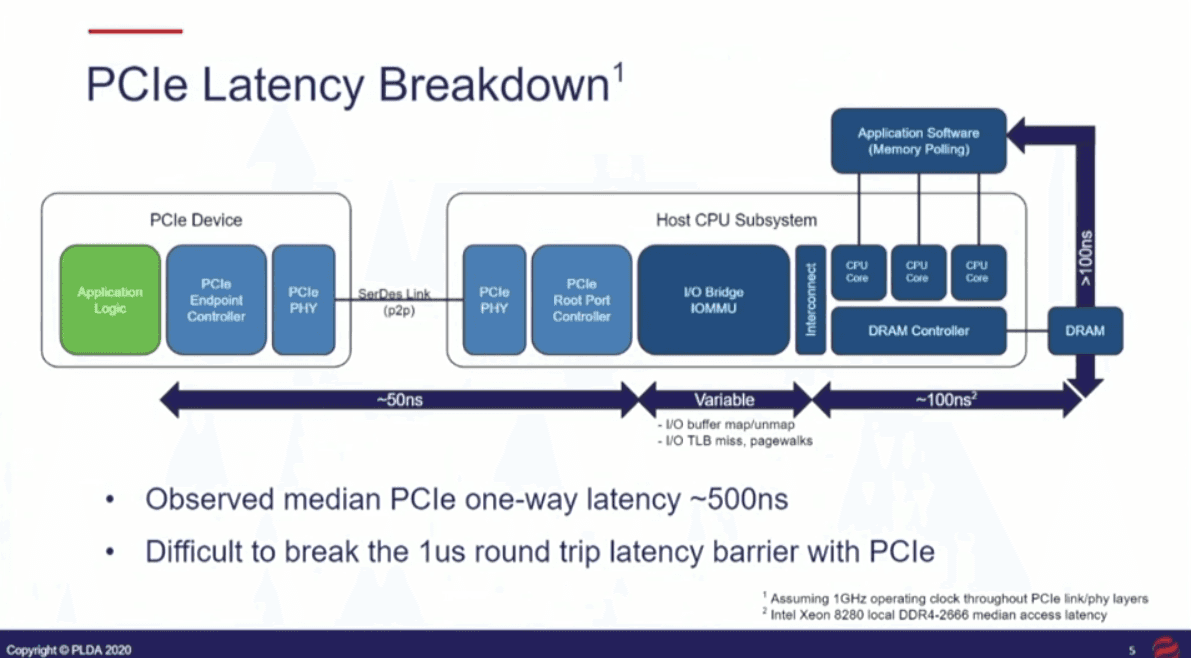

Breaking the PCIe Latency Barrier with CXL

Latency Breakdown

其他子系统

[[ 202309221818321|Address Translation Service ]]

[[ 202312121023023|The throughput of MMIO through PCIe is high ]]

一些研究

- SIGCOMM’18的pcie-bench[1]对PCIe总线在网络中的延迟进行了测试,测得最小延迟是0.8us。

- andre-richter/pcie-lat: Generic x86_64 PCIe latency measurement module for the Linux kernel

相关资料

- wikipedia

- 《深入浅出SSD》第五章 PCIe 介绍

- 深入PCI与PCIe之二:软件篇

- 浅谈PCIe总线(一) - 知乎